在当今数字时代的核心,半导体大规模集成电路(VLSI)作为电子设备的大脑,其性能与可靠性直接决定了从智能手机到数据中心,从自动驾驶汽车到工业控制系统的方方面面。将数以亿计甚至百亿计的晶体管集成在一块微小的芯片上,并确保其出厂时功能完好、性能达标,是一个极其复杂且关键的环节。这正是大规模集成电路测试的核心使命——它是在芯片设计与制造之后、交付给客户之前,守护质量与可靠性的最后一道,也是至关重要的一道防线。

一、测试的必要性与挑战

随着工艺节点不断微缩,芯片复杂度呈指数级增长。制造过程中的微小缺陷,如微粒污染、金属线短路或开路、晶体管阈值电压漂移等,都可能导致芯片功能失效或性能降级。测试的目的就是将这些有缺陷的芯片(称为“瑕疵品”)从大量合格品中筛选出来。其挑战在于:

- 超高复杂度:如何用有限的时间和成本,对内部状态天文数字般的电路进行有效验证?

- 物理限制:芯片的输入/输出引脚数量有限,难以直接观测和控制内部每一个节点。

- 故障模型多样性:故障类型繁多,从固定的“卡在0/1”故障,到更复杂的延时故障、桥接故障等。

- 测试成本压力:测试成本在芯片总成本中的占比日益升高,需要在测试覆盖率、测试时间与成本之间寻求最佳平衡。

二、测试的主要流程与类型

集成电路测试是一个系统化工程,通常贯穿于设计、制造和封装的全过程。

1. 设计阶段:可测试性设计

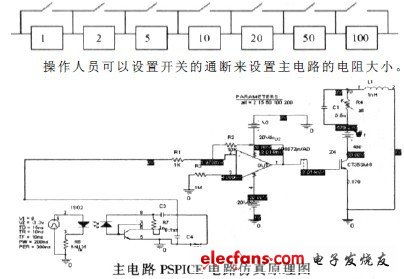

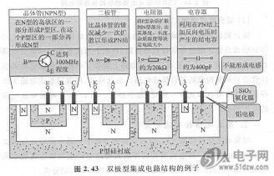

这是测试的基石。为了降低测试难度,工程师会在芯片设计时主动插入可测试性结构,主要包括:

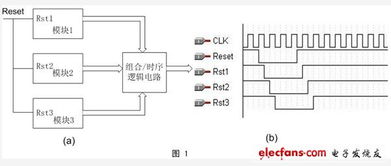

- 扫描链:将芯片内部的时序逻辑单元(触发器)串联成一条或多条链,在测试模式下可以像移位寄存器一样,方便地将测试向量输入、将内部状态输出,极大地提高了内部节点的可控性和可观测性。

- 内建自测试:在芯片内部集成专门的测试电路,使其能够自行生成测试向量、执行测试并分析结果,特别适用于对存储器(如SRAM、DRAM)的测试。

- 边界扫描:主要用于测试芯片之间电路板级的互连,通过IEEE 1149.1(JTAG)标准实现。

2. 制造后测试:核心检测环节

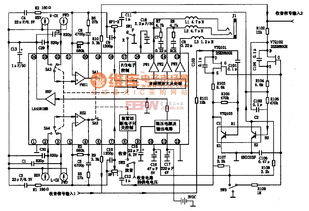

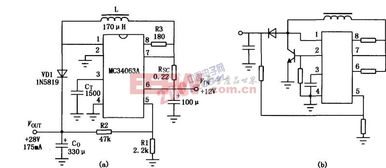

在晶圆制造完成和芯片封装后,会使用昂贵的自动测试设备(ATE)进行严格测试。主要包括:

- 功能测试:验证芯片是否能够正确执行其设计的所有功能。通过输入一系列功能向量,检查输出是否符合预期。这是最基本的测试。

- 参数测试:验证芯片的电气参数是否达标,如供电电流、输入输出电压/电流、信号传输延时、功耗等。这关系到芯片的性能和可靠性。

- 结构测试:不关心具体功能,而是基于故障模型,检测制造中可能引入的物理缺陷。通过向扫描链加载测试向量,可以高效地检测固定型故障。

- 硅片调试与特性测试:对初批芯片进行深入分析,验证其在各种电压、温度角况下的性能极限,为产品标定提供依据。

三、前沿发展与未来趋势

面对先进工艺(如5纳米、3纳米)和新型架构(如Chiplet、3D集成)带来的新挑战,测试技术也在不断演进:

- 基于人工智能的测试优化:利用机器学习算法优化测试向量生成,减少测试集规模,提升故障覆盖率,并预测芯片缺陷。

- 面向系统级芯片的测试:对于集成CPU、GPU、AI加速器、多种IO的复杂SoC,需要协同的层次化测试策略和更高效的测试访问机制。

- 可靠性测试与预测:不仅关注出厂时的好坏,更关注芯片在整个生命周期内的可靠性,如对老化、软错误、热效应的测试与监控。

- 测试安全:防止测试接口成为黑客攻击的后门,确保测试基础设施的安全。

###

半导体大规模集成电路的测试,远非简单的“好坏筛选”。它是一个融合了电路设计、计算机科学、概率统计和精密工程的深度技术领域。正是这些看不见的、严谨而复杂的测试流程,确保了每一颗投入市场的芯片都能稳定、可靠地运行,从而支撑起我们高度数字化的世界。随着芯片继续朝着更复杂、更集成的方向发展,测试技术作为产业背后的“质量守门员”,其重要性只会与日俱增。